电容隔离式栅极驱动电路设计*

来源:优秀文章 发布时间:2023-03-23 点击:

黄晓义,刘天天,赵一泽,俞跃辉,程新红

(1.中国科学院 上海微系统与信息技术研究所 信息与功能材料重点实验室,上海 200050;

2.中国科学院大学 材料科学与光电工程中心,北京 100049)

随着工业电子领域对于电子设备性能要求的不断提升,隔离型栅极驱动芯片正朝小体积、低功耗、速度快等方向快速发展,电感隔离和电容隔离在高频高压的应用场合中逐步取代光耦隔离和高压电平移位隔离[1]。电感隔离利用电磁耦合原理传递磁信号[2],缺点是片上电感占用面积大、抗电磁干扰能力较弱。电容隔离利用耐压电容耦合信号,因具有传输延时短、耐压电压等级高、抗电磁干扰能力强等特点被广泛采用。国外的栅极驱动芯片供应商以ADI(Analog Device Instruments)、TI(Texas Instruments)、Silicon Labs为代表,其中,TI主推电容隔离式栅极驱动芯片,产品以高耐压、寿命长、抗干扰能力强著称[3]。国内对于栅极驱动芯片的研究起步较晚,相比国外无论在研究和商业产品上都有一定的差距。

本文设计了一种电容隔离式的栅极驱动电路,具有低传输延时、高共模瞬态抑制能力(common mode transient immunity,CMTI)、宽工作温度范围等优点,适合用于驱动应用于高频高压领域的绝缘栅双极晶体管(IGBT)和SiC金属氧化物半导体场效应管(MOSFET)功率器件。

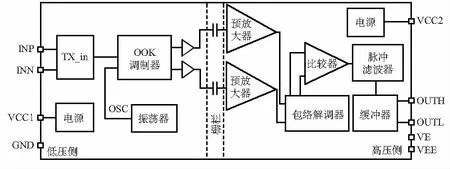

1.1 栅极驱动电路整体架构

基于电容隔离设计了一种栅极驱动电路,整体架构如图1所示,主要包括调制器(modulator)、振荡器(oscillator)、预放大器(pre-amp)、解调器(demodulator)等。

图1 电容隔离式栅极驱动电路设计架构

1.2 信号调制方式

目前普遍使用的信号调制方式有脉冲调制和开关键控(on-off keying,OOK)调制,鉴于电路设计复杂度和对抗噪声性能的考虑,本文采用OOK调制进行信号传输,此调制方式具有中等的静态功耗,抗干扰能力极强[4]。

2.1 振荡器

振荡器(oscillator)模块为栅极驱动电路提供OOK调制所需的载波信号。根据隔离电容大小以及高压侧输入电阻值,设定振荡器的频率为550 MHz,结构采用环形振荡器。不加任何补偿和改进措施的环形振荡器频率随工艺和温度的偏差很大[5],文献[6~8]中提出了针对环形振荡器频率误差的补偿改进措施。本文采取电流匮乏型环形压控振荡器结构并设计了温度补偿措施,在-40~125 ℃温度范围内振荡频率误差小于±2.5 %。

2.2 预放大器

由于信号经过隔离电容传输后会有较大幅度的衰减,预放大器作为高压侧接收的第一级电路需对接收到的信号进行放大。预放大器对增益的要求不高,但是需要较大带宽;

同时放大后为后续解调模块提供全差分信号,本文设计中预放大器采用3级级联的开环运放结构。预放大器结构参考宽带放大器设计思路[9~11],电路原理如图2,每一级均为带有源电感负载的共源级差分放大结构。为增强栅极驱动电路高压侧信号接收模块的抗噪声干扰能力,本文设计的预放大器需具备较大带宽以放大高频信号,同时对除了高频载波频段以外的信号进行抑制。OOK调制中的高频载波为550 MHz,因此,利用有源电感负载将预放大器的放大能力尖峰设置在此频率附近。

图2 预放大器电路原理

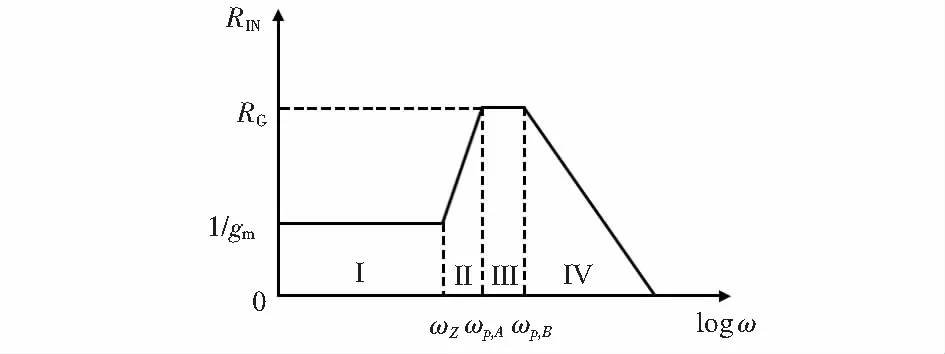

图3给出了有源电感负载的电路原理及小信号等效模型,分析有源电感负载的原理与设计过程。图3(a)中RIN是从M1管漏端看进去的等效阻抗,RG为跨接在栅、漏两端的电阻,CGS为栅—源电容,CDS为漏—源电容。

图3 有源电感负载

通过小信号等效模型推导RIN零极点位置和表达式为

ωZ=1/RGCGS,ωP,A=gm/CGS,ωP,B=1/RGCDS

(1)

(2)

得到有源电感负载等效阻抗的频率特性曲线如图4。

图4 输入电阻随频率变化曲线

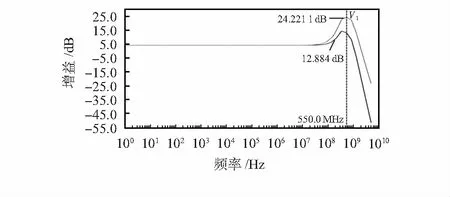

预放大器的第3级结构与前2级有所不同,目的是利用不同的栅极电阻RG产生2组放大幅值不同的差分信号,以备后续解调。预放大器的幅频特性仿真曲线如图5,利用不同的栅极电阻RG产生了放大倍数的差异且两条增益曲线均在载波频率550 MHz存在放大能力的尖峰。

图5 预放大器仿真波形

2.3 解调器

图6是一种传统的包络检波解调器结构[12],Vin+和Vin-为经过预放大器放大后的差分信号,通过M1,M2交替导通对电容CL充电,电流源给电容CL提供电荷泄放路径,并提供稳定的直流电平。

图6 传统包络检测电路

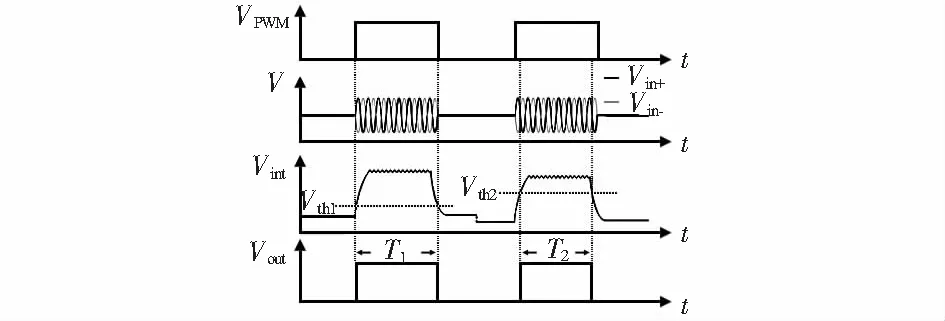

Vint为一馒头波形状信号,与判决阈值Vth比较后整形为方波。图7描述了信号解调过程中脉冲宽度失真的产生原理,当判决阈值Vth或信号Vint直流电平由于工艺角和温度的影响产生了相对位置的变化,导致解调后信号的脉冲宽度从T1变化至T2,相较于原先的控制信号VPWM产生了脉冲宽度的偏差。

图7 传统包络解调引起的脉冲宽度失真

图8为本文提出的改进型解调方案,分别对2组差分信号进行包络检测,以其中一组解调产生的馒头波信号作为判决阈值替代传统的检测模式。预放大器在最后一级产生了2组不同幅值的全差分信号,将2组信号A1,A2,B1,B2分别进行解调得到2个最大幅值不同的馒头波信号V1,V2,电阻R用来产生V1与V2两信号的直流电平差值。

图8 本文提出的包络检测架构

改进型包络解调的工作波形如图9所示,此方案中2个波形V1,V2随工艺和温度的幅值偏移是同方向的,因此可以减小引起的脉宽失真,将其输入到比较器中即可还原控制信号。

图9 提出的包络检测方案波形示意

此外,改进型包络解调结构无须设计判决阈值电压Vth,减轻电路设计复杂度。在不同工艺角和温度的55个组合下对2种解调结构进行仿真对比,结果如图10所示。将脉冲宽度失真按照2 ns划分成5个区间段,横坐标代表脉冲宽度失真,纵坐标代表每一区间段的占比,仿真结果表明,改进型包络解调结构可整体降低脉冲宽度失真。

图10 不同工艺角下脉宽失真对比

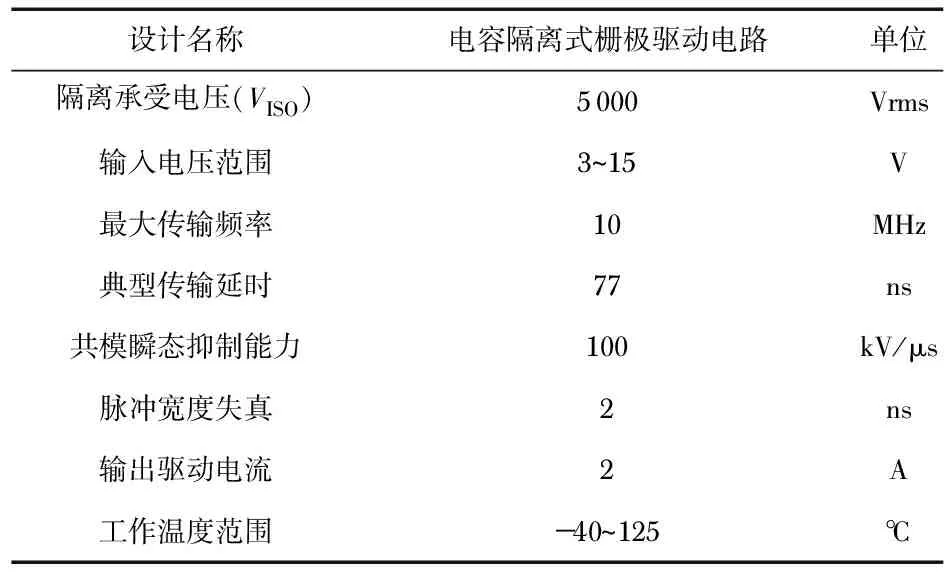

基于X-FAB 0.35 μm工艺,绘制栅极驱动电路版图,进行后仿真验证,结果汇总如表1。

表1 后仿真主要性能参数

为验证本文所设计的栅极驱动电路的实用性,在Cadence中搭建双脉冲测试仿真电路,仿真使用的SiC MOSFET模型为Rohm公司的1 200 V/55A的SCT3040KR。输入驱动信号为1 MHz,占空比50 %的方波信号,仿真结果如图11。

图11 双脉冲仿真开关波形

功率器件栅—源电压VGS即栅极驱动电路输出低电平为-5 V,高电平为20 V;

米勒平台时长约为80 ns;

漏—源电压VDS浮动于母线电压600 V与地之间,SiC MOSFET的开通关断时间均小于0.1 μs;

电流IDS可正常完成续流。

本文设计了一种电容隔离式栅极驱动电路,进行了版图绘制以及后仿真验证。驱动电路具有传输延时低、共模瞬态抑制能力强等特点,可驱动应用于高频高压领域的IGBT和SiC MOSFET功率器件。

猜你喜欢 栅极电感电容 离子推力器三栅极组件热形变仿真分析及试验研究真空与低温(2022年2期)2022-03-30浅析投射式多点触控电容触摸屏电子制作(2018年19期)2018-11-14基于NCP1608B的PFC电感设计通信电源技术(2018年5期)2018-08-23基于耦合电感的自均流LLC谐振变换器的设计通信电源技术(2018年5期)2018-08-23栅极液压成型专用设备的研制制造技术与机床(2017年10期)2017-11-28宽电容测量仪的设计电子制作(2017年7期)2017-06-05基于双重软开关Buck变换器的超级电容充电电源电测与仪表(2016年10期)2016-04-12集成耦合电感升压-反激变换器的性能研究电测与仪表(2016年12期)2016-04-11电感耦合等离子体发射光谱法在钒、钛分析中的应用河北地质(2016年4期)2016-03-20金属钼栅极高温定型处理技术研究真空与低温(2015年6期)2015-11-04推荐访问:栅极 电容 隔离